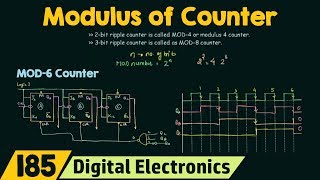

Counters || Asynchronous || Synchronous || Verilog Codes of Counters ||

Вставка

- Опубліковано 12 січ 2025

- #tmsy #verilog #DSDV

Digital Counter is a set of flip-flops whose states change in response to the pulse applied at the input to the Counter.

The output is the binary Equivalent of the Total Number of pulses that have occurred up to that time.

Thus as its name implies, a Counter is used to count pulses.

A Counter Can also be used as a frequency divider

A Counter is used to Count the Number of clock pulses arriving at its input.

Asynchronous [Ripple]

The Flip Flops are connected in such a way that the output of 1st FF Drives the clock for the 2nd FF; the Output of 2nd Drives 3rd & So…on.

All the FF’s are not Clocked Simultaneously.

Design and Implementation is Very Simple Even for More Number of States.

Low Speed

Synchronous

There is No Connection between the Output of 1st FF and Clock Input of Next FF.

All the Flip-flops are Clocked Simultaneously.

Design becomes Difficult if the Number of States increased.

High Speed.

EDA PlayGround:

www.edaplaygro...

Facebook: / tmsy.tutorials

Instagram: / tmsy_tutorials

Website: www.tmsytutori...

Thank you sir😊

Thanks sir🤗

Thanks a lot sir

if i have to use the counter till 1100 rather than 1111, what'd be the changes?

Sir, can you please tell for any verilog question how to find out the total number of inputs, output and control signal ports to write the program? For example 2x4 decoder we can realise it with enable signal or without enable signal, but how to find at what condition we have to use that certain type of circuit?

If u want to realise any higher order circuits from lower order then it's mandatory to use enable. Example 3x8 decoder using 2x4 decoder....

Recently got a question to realise a 64 bit arithmetic shift register which can shift either 1 time or 8 time. In this question later I got to know that enable signal has to be used. How to find out these things sir? Pls help

Please can you explain asynchronous active low reset and asynchronous active high reset? What is the value of reset 0,1 Please i have exam

ua-cam.com/video/Nvg86suzZbY/v-deo.html

Go through this once